13. Appendix¶

Note

NC => Not connected, IO => Input and output

13.1. ECLK signals on FMC¶

| lpGBT signal | FMC Pin | VLDB+ signal direction | Total routed length (mm) |

|---|---|---|---|

| ECLK0P | NC (SMA) | Output | 61.433 |

| ECLK0N | NC (SMA) | Output | 61.376 |

| ECLK1P | J1 - D8 | Output | 69.522 |

| ECLK1N | J1 – D9 | Output | 69.265 |

| ECLK2P | J1 – G27 | Output | 68.442 |

| ECLK2N | J1 – G28 | Output | 68.138 |

| ECLK3P | J1 – H34 | Output | 69.746 |

| ECLK3N | J1 – H35 | Output | 69.123 |

| ECLK4P | J1 – D20 | Output | 69.217 |

| ECLK4N | J1 – D21 | Output | 69.005 |

| ECLK5P | J1 – H19 | Output | 68.900 |

| ECLK5N | J1 – H20 | Output | 68.689 |

| ECLK6P | J1 – G24 | Output | 69.627 |

| ECLK6N | J1 – G25 | Output | 69.074 |

| ECLK7P | J1 – C18 | Output | 69.509 |

| ECLK7N | J1 – C19 | Output | 69.509 |

| ECLK8P | J1 – H16 | Output | 69.900 |

| ECLK8N | J1 – H17 | Output | 69.304 |

| ECLK9P | J1 – G15 | Output | 70.256 |

| ECLK9N | J1 – G16 | Output | 69.768 |

| ECLK10P | J1 – D14 | Output | 70.258 |

| ECLK10N | J1 – D15 | Output | 69.662 |

| ECLK11P | J1 – C14 | Output | 69.580 |

| ECLK11N | J1 – C15 | Output | 68.626 |

| ECLK12P | J1 – D11 | Output | 69.133 |

| ECLK12N | J1 – D12 | Output | 68.319 |

| ECLK13P | J1 – H13 | Output | 69.776 |

| ECLK13N | J1 – H14 | Output | 69.180 |

| ECLK14P | J1 – G12 | Output | 70.350 |

| ECLK14N | J1 – G13 | Output | 69.761 |

| ECLK15P | J1 – H10 | Output | 68.473 |

| ECLK15N | J1 – H11 | Output | 67.881 |

| ECLK16P | J2 – H25 | Output | 105.114 |

| ECLK16N | J2 – H26 | Output | 106.056 |

| ECLK17P | J2 – G24 | Output | 102.544 |

| ECLK17N | J2 – G25 | Output | 103.486 |

| ECLK18P | J2 – D23 | Output | 102.489 |

| ECLK18N | J2 – D24 | Output | 101.893 |

| ECLK19P | J2 – C14 | Output | 101.942 |

| ECLK19N | J2 – C15 | Output | 100.498 |

| ECLK20P | J2 – C22 | Output | 101.978 |

| ECLK20N | J2 – C23 | Output | 103.188 |

| ECLK21P | J2 – C10 | Output | 101.179 |

| ECLK21N | J2 – C11 | Output | 99.765 |

| ECLK22P | J2 – H16 | Output | 101.003 |

| ECLK22N | J2 – H17 | Output | 99.948 |

| ECLK23P | J2 – H10 | Output | 105.727 |

| ECLK23N | J2 – H11 | Output | 103.827 |

| ECLK24P | J2 – C18 | Output | 104.896 |

| ECLK24N | J2 – C19 | Output | 104.510 |

| ECLK25P | J2 – G9 | Output | 101.293 |

| ECLK25N | J2 – G10 | Output | 101.239 |

| ECLK26P | J2 – G6 | Output | 102.243 |

| ECLK26N | J2 – G7 | Output | 101.125 |

| ECLK27P | J2 – H22 | Output | 101.974 |

| ECLK27N | J2 – H23 | Output | 101.188 |

| ECLK28P | NC (mHDMI) | Output | 141.018 |

| ECLK28N | NC (mHDMI) | Output | 139.991 |

13.2. EDIN signals on FMC¶

| lpGBT signal | FMC Pin | VLDB+ signal direction | Total routed length (mm) |

|---|---|---|---|

| EDIN00P | J1 – C26 | Input | 78.894 |

| EDIN00N | J1 – C27 | Input | 78.432 |

| EDIN01P | J1 – H31 | Input | 78.728 |

| EDIN01N | J1 – H32 | Input | 78.360 |

| EDIN02P | J1 – H28 | Input | 79.154 |

| EDIN02N | J1 – H29 | Input | 78.704 |

| EDIN03P | J1 – G33 | Input | 78.485 |

| EDIN03N | J1 – G34 | Input | 77.871 |

| EDIN10P | J1 – G36 | Input | 79.446 |

| EDIN10N | J1 – G37 | Input | 78.571 |

| EDIN11P | J1 – H37 | Input | 78.972 |

| EDIN11N | J1 – H38 | Input | 78.077 |

| EDIN12P | J1 – D26 | Input | 78.455 |

| EDIN12N | J1 – D27 | Input | 77.956 |

| EDIN13P | J1 – H25 | Input | 78.771 |

| EDIN13N | J1 – H26 | Input | 78.281 |

| EDIN20P | J1 – G21 | Input | 78.642 |

| EDIN20N | J1 – G22 | Input | 77.815 |

| EDIN21P | J1 – H22 | Input | 78.473 |

| EDIN21N | J1 – H23 | Input | 77.767 |

| EDIN22P | J1 – G18 | Input | 78.366 |

| EDIN22N | J1 – G19 | Input | 77.458 |

| EDIN23P | J1 – D17 | Input | 78.721 |

| EDIN23N | J1 – D18 | Input | 77.905 |

| EDIN30P | J1 – C10 | Input | 78.983 |

| EDIN30N | J1 – C11 | Input | 77.861 |

| EDIN31P | J1 – G9 | Input | 80.345 |

| EDIN31N | J1 – G10 | Input | 79.537 |

| EDIN32P | J1 – H7 | Input | 78.818 |

| EDIN32N | J1 – H8 | Input | 77.672 |

| EDIN33P | J1 – G6 | Input | 80.894 |

| EDIN33N | J1 – G7 | Input | 80.031 |

| EDIN40P | J2 – D8 | Input | 111.183 |

| EDIN40N | J2 – D9 | Input | 109.908 |

| EDIN41P | J2 – D17 | Input | 112.909 |

| EDIN41N | J2 – D18 | Input | 111.722 |

| EDIN42P | J2 – G18 | Input | 113.348 |

| EDIN42N | J2 – G19 | Input | 112.135 |

| EDIN43P | J2 – G15 | Input | 113.891 |

| EDIN43N | J2 – G16 | Input | 112.660 |

| EDIN50P | J2 – H19 | Input | 111.447 |

| EDIN50N | J2 – H20 | Input | 110.178 |

| EDIN51P | J2 – D14 | Input | 111.517 |

| EDIN51N | J2 – D15 | Input | 110.119 |

| EDIN52P | J2 – H13 | Input | 111.428 |

| EDIN52N | J2 – H14 | Input | 110.134 |

| EDIN53P | J2 – G12 | Input | 112.653 |

| EDIN53N | J2 – G13 | Input | 111.325 |

| EDIN60P | J2 – D20 | Input | 111.708 |

| EDIN60N | J2 – D21 | Input | 110.393 |

| EDIN61P | J2 – G21 | Input | 113.926 |

| EDIN61N | J2 – G22 | Input | 111.301 |

| EDIN62P | J2 – H7 | Input | 112.285 |

| EDIN62N | J2 – H8 | Input | 111.031 |

| EDIN63P | J2 – D11 | Input | 112.821 |

| EDIN63N | J2 – D12 | Input | 111.497 |

13.3. EDOUT signals on FMC¶

| lpGBT signal | FMC Pin | VLDB+ signal direction | Total routed length (mm) |

|---|---|---|---|

| EDOUT00P | J1 – F16 | Output | 95.576 |

| EDOUT00N | J1 – F17 | Output | 95.152 |

| EDOUT01P | J1 – E15 | Output | 95.542 |

| EDOUT01N | J1 – E16 | Output | 95.333 |

| EDOUT02P | J1 – J15 | Output | 94.944 |

| EDOUT02N | J1 – J16 | Output | 94.707 |

| EDOUT03P | J1 – F13 | Output | 95.576 |

| EDOUT03N | J1 – F14 | Output | 95.397 |

| EDOUT10P | J1 – K13 | Output | 95.018 |

| EDOUT10N | J1 – K14 | Output | 95.125 |

| EDOUT11P | J1 – J12 | Output | 95.968 |

| EDOUT11N | J1 – J13 | Output | 96.009 |

| EDOUT12P | J1 – E12 | Output | 95.224 |

| EDOUT12N | J1 – E13 | Output | 94.987 |

| EDOUT13P | J1 – F10 | Output | 95.837 |

| EDOUT13N | J1 – F11 | Output | 96.056 |

| EDOUT20P | J1 – K10 | Output | 95.605 |

| EDOUT20N | J1 – K11 | Output | 94.617 |

| EDOUT21P | J1 – J9 | Output | 97.226 |

| EDOUT21N | J1 – J10 | Output | 96.246 |

| EDOUT22P | J1 – F7 | Output | 99.674 |

| EDOUT22N | J1 – F8 | Output | 98.750 |

| EDOUT23P | J1 – K7 | Output | 95.047 |

| EDOUT23N | J1 – K8 | Output | 94.091 |

| EDOUT30P | J1 – J6 | Output | 97.015 |

| EDOUT30N | J1 – J7 | Output | 96.035 |

| EDOUT31P | J1 – E6 | Output | 100.963 |

| EDOUT31N | J1 – E7 | Output | 99.839 |

| EDOUT32P | J1 – F4 | Output | 97.866 |

| EDOUT32N | J1 – F5 | Output | 96.839 |

| EDOUT33P | J1 – E2 | Output | 100.990 |

| EDOUT33N | J1 – E3 | Output | 100.002 |

13.4. PSCLK signals on FMC¶

| lpGBT signal | FMC Pin | VLDB+ signal direction | Total routed length (mm) |

|---|---|---|---|

| PSCLK0P | J2 – H37 | Output | 57.026 |

| PSCLK0N | J2 – H38 | Output | 57.091 |

| PSCLK1P | NC (SMA) | Output | 66.228 |

| PSCLK1N | NC (SMA) | Output | 66.314 |

| PSCLK2P | J2 – H34 | Output | 54.005 |

| PSCLK2N | J2 – H35 | Output | 53.673 |

| PSCLK3P | J2 – H31 | Output | 53.325 |

| PSCLK3N | J2 – H32 | Output | 52.081 |

13.5. Slow Control signals on FMC¶

| lpGBT signal | FMC Pin | VLDB+ signal direction |

|---|---|---|

| ADC0 | J2 – J9 | Input |

| ADC1 | J2 – J10 | Input |

| ADC2 | J2 – F10 | Input |

| ADC3 | J2 – F11 | Input |

| ADC4 | J2 – E9 | Input |

| ADC5 | J2 – E10 | Input |

| ADC6 | J2 – K13 | Input |

| ADC7 | J2 – K14 | Input |

| VDAC | J2 – J12 | Output |

| GPIO0 | J2 – J13 | IO |

| GPIO1 | J2 – F13 | IO |

| GPIO2 | J2 – F14 | IO |

| GPIO3 | J2 – E12 | IO |

| GPIO4 | J2 – E13 | IO |

| GPIO5 | J2 – J15 | IO |

| GPIO6 | J2 – J16 | IO |

| GPIO7 | J2 – F16 | IO |

| GPIO8 | J2 – F17 | IO |

| GPIO9 | J2 – E15 | IO |

| GPIO10 | J2 – E16 | IO |

| GPIO11 | J2 – K16 | IO |

| GPIO12 | J2 – K17 | IO |

| GPIO13 | J2 – J18 | IO |

| GPIO14 | J2 – J19 | IO |

| GPIO15 | J2 – K22 | IO |

| RSTOUTB | J2 – K23 | Output |

| MSCL0 | J2 – E18 | Output |

| MSDA0 | J2 – E19 | IO |

| MSCL1 | J2 – K19 | Output |

| MSDA1 | J2 – K20 | IO |

| MSCL2 | J2 – J21 | Output |

| MSDA2 | J2 – J22 | IO |

Note

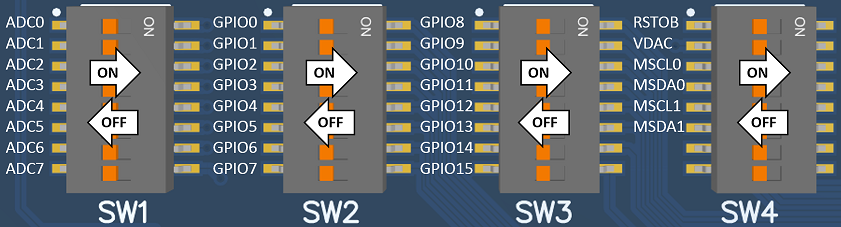

The above connections are only true when SW1, SW2, SW3 and SW4 are enabled and no jumper is put on W3..W15.

Warning

No jumpers must be put on W3..W15 when the FMC switches are enabled.

13.6. Miscellaneous signals on FMC¶

| FPGA Evaluation Kit signal | Parameter | FMC Pin | VLDB+ signal direction | Value (V) |

|---|---|---|---|---|

| VADJ | FPGA Evaluation Kit Voltage adjust | J1 – E39 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J1 – F40 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J1 – G39 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J1 – H40 | Input | 1.2 |

| HPC1_VIO_B_M2C | Mezzanine to carrier supply voltage | J1 – J39 | Output | 1.2 |

| HPC1_VIO_B_M2C | Mezzanine to carrier supply voltage | J1 – K40 | Output | 1.2 |

| HPC1_VREF_A_M2C | Mezzanine to carrier A reference voltage | J1 – H1 | Output | 0.6 |

| HPC1_VREF_B_M2C | Mezzanine to carrier B reference voltage | J1 – K1 | Output | 0.6 |

| HPC1_PRSNTM2C_L | Mezzanine to carrier module present signal | J1 – H1 | Output | 0 |

| P12V0_FMC | FMC Evaluation Kit power supply | J1 – C35 | Input | 12 |

| P12V0_FMC | FMC Evaluation Kit power supply | J1 – C37 | Input | 12 |

| HPC1_PG_M2C | Mezzanine to carrier powergood voltage | J1 – F1 | Output | 2.5 |

| HPC1_PG_C2M | Mezzanine to carrier powergood voltage | J1 - D1 | Input | 3.3 (NC on the VLDB+) |

| VADJ | FPGA Evaluation Kit Voltage adjust | J1 – E39 | Input | 1.2 |

| HPC1_GA0 | Geographic Address 1 for EEPROM | J1 – C34 | Input | 0 (VC707) |

| HPC1_GA1 | Geographic Address 2 for EEPROM | J1 – D35 | Input | 0 (VC707) |

| HPC1_SCL | I2C Clock | J1 – C30 | Input | 3.3 |

| HPC1_SDA | I2C Bi-directional serial data | J1 – C31 | IO | 3.3 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J2 – E39 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J2 – F40 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J2 – G39 | Input | 1.2 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J2 – H40 | Input | 1.2 |

| HPC2_VIO_B_M2C | Mezzanine to carrier supply voltage | J2 – J39 | Output | 1.2 |

| HPC2_VIO_B_M2C | Mezzanine to carrier supply voltage | J2 – K40 | Output | 1.2 |

| HPC2_VREF_A_M2C | Mezzanine to carrier A reference voltage | J2 – H1 | Output | 0.6 |

| HPC2_VREF_B_M2C | Mezzanine to carrier B reference voltage | J2 – K1 | Output | 0.6 |

| HPC2_PRSNTM2C_L | Mezzanine to carrier module present signal | J2 – H1 | Output | 0 (NC on the VLDB+) |

| P12V0_FMC | FMC Evaluation Kit power supply | J2 – C35 | Input | 12 |

| P12V0_FMC | FMC Evaluation Kit power supply | J2 – C37 | Input | 12 |

| HPC2_PG_M2C | Mezzanine to carrier powergood voltage | J2 – F1 | Output | 0 |

| HPC2_PG_C2M | Mezzanine to carrier powergood voltage | J2 - D1 | Input | 3.3 |

| VADJ | FPGA Evaluation Kit Voltage adjust | J2 – E39 | Input | 1.2 |

| P3V3_FMC | FMC power supply | J2 – C39 | Input | 3.3 |

| P3V3_FMC | FMC power supply | J2 – D38 | Input | 3.3 |

| P3V3_FMC | FMC power supply | J2 – D40 | Input | 3.3 |

Note

For more information about the FMC signals, refer to the ANSI VITA57.1 standard.

13.7. Protection switches¶

FMC Switches (SW1..SW4) |

lpGBT signal |

|---|---|

| SW1 - 1 | ADC0 |

| SW1 - 2 | ADC1 |

| SW1 - 3 | ADC2 |

| SW1 - 4 | ADC3 |

| SW1 - 5 | ADC4 |

| SW1 - 6 | ADC5 |

| SW1 - 7 | ADC6 |

| SW1 - 8 | ADC7 |

| SW2 - 1 | GPIO0 |

| SW2 - 2 | GPIO1 |

| SW2 - 3 | GPIO2 |

| SW2 - 4 | GPIO3 |

| SW2 - 5 | GPIO4 |

| SW2 - 6 | GPIO5 |

| SW2 - 7 | GPIO6 |

| SW2 - 8 | GPIO7 |

| SW3 - 1 | GPIO8 |

| SW3 - 2 | GPIO9 |

| SW3 - 3 | GPIO10 |

| SW3 - 4 | GPIO11 |

| SW3 - 5 | GPIO12 |

| SW3 - 6 | GPIO13 |

| SW3 - 7 | GPIO14 |

| SW3 - 8 | GPIO15 |

| SW4 - 1 | RSTOUTB |

| SW4 - 2 | VDAC |

| SW4 - 3 | MSCL0 |

| SW4 - 4 | MSDA0 |

| SW4 - 5 | MSCL1 |

| SW4 - 6 | MSDA1 |

| SW4 - 7 | NC |

| SW4 - 8 | NC |

13.8. lpGBT configuration pins¶

13.8.1. VLDB+ V1.1 (lpGBT V0)¶

| lpGBT signal | VLDB+ connection | lpGBT signal direction |

|---|---|---|

| ADR[3..0] | SW6 - [1 - 4] | Input |

| MODE[3..0] | SW7 - [1 - 4] or Raspberry Pi Control J13 | Input |

| SC_I2C | SW8 - 1 | Input |

| LOCKMODE | SW8 - 2 | Input |

| STATEOVRD | SW8 - 3 | Input |

| PORDIS | SW8 - 4 | Input |

| RSTB | Push Button PB1 and Raspberry Pi Control J13 | Input |

13.8.2. VLDB+ V2 with lpGBT V0¶

| lpGBT signal | VLDB+ connection | lpGBT signal direction |

|---|---|---|

| ADR[3..0] | SW6 - [1 - 4] | Input |

| MODE[3..0] | SW7 - [1 - 4] or Raspberry Pi Control J13 | Input |

| VCOBYPASS | SW8 - 1 | Input |

| SC_I2C | SW8 - 2 | Input |

| LOCKMODE | SW8 - 3 | Input |

| STATEOVRD | SW8 - 4 | Input |

| PORDIS | SW8 - 5 | Input |

| RSTB | Push Button PB1 and Raspberry Pi Control J13 | Input |

13.8.3. VLDB+ V2 with lpGBT V1¶

| lpGBT signal | VLDB+ connection | lpGBT signal direction |

|---|---|---|

| ADR[3..0] | SW6 - [1 - 4] | Input |

| MODE[3..0] | SW7 - [1 - 4] or Raspberry Pi Control J13 | Input |

| BOOTCNF0 | SW8 - 1 | Input |

| BOOTCNF1 | SW8 - 2 | Input |

| LOCKMODE | SW8 - 3 | Input |

| EDINECTERM | SW8 - 4 | Input |

| PORDIS | SW8 - 5 | Input |

| RSTB | Push Button PB1 and Raspberry Pi Control J13 | Input |

Note

The control of the Mode[3..0] is ruled by the Raspberry PI when it’s connected and properly configured by the piGBT web.

For more information, please look at the piGBT manual.

13.9. lpGBT I2C pull-ups¶

| Pull-up switch | lpGBT signal |

|---|---|

| SW5 - 1 | SLSCL |

| SW5 - 2 | SLSDA |

| SW5 - 3 | MSCL[0] |

| SW5 - 4 | MSDA[0] |

| SW5 - 5 | MSCL[1] |

| SW5 - 6 | MSDA[1] |

| SW5 - 7 | NC |

| SW5 - 8 | NC |

Note

When using the RPI Control Toolkit, no SLSCL and SLSDA pull-ups are neccesary since the Control Toolkit already features them.

13.10. High speed signals¶

| lpGBT signal | VLDB+ connection | VLDB+ signal direction | Total routed length (mm) |

|---|---|---|---|

| HSOUTP | VTRx+ TX1N | Output | 4.231 |

| HSOUTN | VTRx+ TX1P | Output | 4.242 |

| HSINP | VTRx+ RX1P | Input | 4.137 |

| HSINN | VTRx+ RX1N | Input | 4.129 |

Note

HSOUT polarity is inverted by purpose to ease the layout. It can be re-swapped through the lpGBT’s

[0x036] ChipConfig register for the V0

and [0x036] ChipAdr for the V1 (also through IC).

13.11. Slow control signals on VLDB+¶

| lpGBT signal | VLDB+ connection | VLDB+ signal direction |

|---|---|---|

| ADC0 | VTRx+ RSSI | Input |

| ADC1 | VTRx+ temperature sensor | Input |

| ADC2 | lpGBT’s DAC | Input |

| ADC3 | 1kΩ potentiometer | Input |

| ADC4 | PT1000 sensor | Input |

| ADC5 | P2V5 monitoring | Input |

| ADC6 | VIN monitoring | Input |

| VDAC | lpGBT’s ADC2/W1-1 | Output |

| GPIO0 | VTRx+ DISABLE | Output |

| GPIO1 | VTRx+ RESET | Output |

| GPIO2 | DC/DC 1.2V PG | Input |

| GPIO3 | DC/DC 2.5V PG | Input |

| GPIO4 | SW11 | Input |

| GPIO5 | LED LD6 | Output |

| MSCL2 | VTRx+ I2C SDA | Output |

| MSDA2 | VTRx+ I2C SCL | IO |

| ECLK28P/N | mHDMI J12 | Output |

| EDOUTECP/N | mHDMI J12 | Output |

| EDINECP/N | mDHMI J12 | Input |

| PSCLK1P/N | J6/7 SMA connectors | Output |

| TSTOUT[3..0] | J10 CCH-04 | Output |

| DIFFTSTOUT[5..4]P/N | J11 CCH-04 | Output |

| TSTCLKINP/N | NC | NC |

13.12. VLDB+ switches¶

| Connector | Function |

|---|---|

| SW1 | Switch for lpGBT’s ADC[7..0]-FMC connection |

| SW2 | Switch for lpGBT’s GPIO[7..0]-FMC connection |

| SW3 | Switch for lpGBT’s GPIO[15..8]-FMC connection |

| SW4 | Switch for lpGBT’s RSTOUTB/VDAC/MSCL[1..0]/MSDA[1..0]-FMC connection |

| SW5 | I2C optional pull-ups. For lpGBT’s MSCL/MSDA[1..0] and SLSDA/SLSCL |

| SW6 | Selects the address of the lpGBT. lpGBT’s I2C address = 111 + SW3 address |

| SW7 | Selects the mode of the lpGBT |

| SW8 | Selects several modes of operation of the lpGBT: VCOBYPASS/BOOTCNF0, SCI2C/BOOTCNF1, LOCKMODE, STATEOVRD/EDINECTERM and PORDIS |

| SW9 | On-Off switch for lpGBT’s GPIO4 input |

| SW10 | VLDB+ power on switch. Shift the switch to the top for FMC mode and to bottom for Standalone mode |

13.13. VLDB+ jumpers¶

| Connector | Function | Left pin | Right pin |

|---|---|---|---|

| W1 | lpGBT´s DAC to probe with a multimeter | VDAC | GND |

| W2 | RSSI voltage adapter value | 2V5 | 1V2 |

| W3 | ADC0 - Adapted VTRx+ RSSI | ADC0 | Adapted VTRx+ RSSI (=ADC0*0.32) |

| W4 | ADC1 – lpGBT temperature sensor | ADC1 | VTRx+ TH10000 |

| W5 | ADC2 – lpGBT VDAC | ADC2 | VDAC |

| W6 | ADC3 – VLDB+ potentiometer | ADC3 | P5 |

| W7 | ADC4 – VLDB+ temperature sensor | ADC4 | PT1000 |

| W8 | ADC5 – Adapted FEASTMP 2.5V output | ADC5 | Adapted FEASTMP2.5 output (=ADC5/3) |

| W9 | ADC6 – Adapted VLDB+ voltage input | ADC6 | Adapted VLDB+ VIN (=ADC6*0.068) |

| W10 | GPIO0 – Disable VTRx+ | GPIO0 | VTRx+ disable |

| W11 | GPIO1 – Reset VTRx+ | GPIO1 | VTRx+ reset |

| W12 | GPIO2 – FEASTMP1.2 power good | GPIO2 | FEASTMP1.2 PG |

| W13 | GPIO3 – FEASTMP2.5 power good | GPIO3 | Adapted FEASTMP2.5 PG (=GPIO3/2) |

| W14 | GPIO4 – VLDB+ switch | GPIO4 | SW9 |

| W15 | GPIO5 – VLDB+ LED | GPIO5 | T4 - LED5 (transistor + LED) |

| W16 | Connect RPI J2 2.5V to it for fusing | VDDF2V5 | NC |

| Connector | Function | Left pin | Right pin |

|---|---|---|---|

| W1 | lpGBT´s DAC to probe with a multimeter | VDAC | GND |

Note

The W1 2-pin connector is not meant to put a jumper on it but a multimeter probe.

13.14. VLDB+ connectors¶

| Connector | Function |

|---|---|

| J1 | FMC HPC1 to connect to an FPGA Evaluation Kit or Front-end detector |

| J2 | FMC HPC2 to connect to an FPGA Evaluation Kit or Front-end detector |

| J3 | Phoenix 1757242 connector to provide external power 10V-12V using the pluggable Phoenix 1757019 connector. |

| J4 | lpGBT’s reference clock SMA input, N pair |

| J5 | lpGBT’s reference clock SMA input, P pair |

| J6 | lpGBT’s phase shifter clock SMA output, P pair |

| J7 | lpGBT’s phase shifter clock SMA output, N pair |

| J8 | lpGBT’s eclk 0 SMA output, P pair |

| J9 | lpGBT’s eclk 0 SMA output, N pair |

| J10 | CCH-J-04 connector for lpGBT’s TSTOUT signals (not mounted) |

| J11 | CCH-J-04 connector for lpGBT’s differential TSTOUT signals (not mounted) |

| J12 | Mini HDMI connector for lpGBT-SCA communication with an external VLDB |

| J13 | Raspberry PI connector for lpGBT’s i2c configuration programming |

| J14 | HIROSE DF40HC(4.0)-40DS-0.4V connector to plug the VTRx+ on it |

| FEASTMP1.2 | SAMTEC SFM-106-01-L-D-A, connector for the FEASTMP1.2V |

| FEASTMP2.5 | SAMTEC SFM-106-01-L-D-A, connector for the FEASTMP2.5V |

13.15. VLDB+ push buttons¶

| Push Button | Function |

|---|---|

| PB1 | lpGBT´s RSTB input. When pressing, resets the lpGBT |

| PB2 | NC |

Note

In the VLDB V1.1 only, if the PiGBT is connected, no reset is performed when pressing the PB1.

13.16. VLDB+ testpoints¶

| Testpoint | Connection |

|---|---|

| GND[1..6] | VLDB+ common ground |

| P1V2lpGBT | lpGBT P1V2 input supply |

| VREF | lpGBT’s reference voltage pin |

| P1V2 | FEASTMP1V2 output voltage |

| 1V2PG | FEASTMP1V2 power good output voltage |

| P2V5 | FEASTMP2V5 output voltage |

| 2V5PG | FEASTMP2V5 power good output voltage |

| RSTB | lpGBT’s RSTB pin |

| SLSCL | SCL pin of the lpGBT’s I2C slave interface |

| SLSDA | SDA pin of the lpGBT’s I2C slave interface |

| MSCL0 | SCL0 pin of the lpGBT’s I2C master interface |

| MSDA0 | SDA0 pin of the lpGBT’s I2C master interface |

| MSCL1 | SCL1 pin of the lpGBT’s I2C master interface |

| MSDA1 | SDA1 pin of the lpGBT’s I2C master interface |

| VTRX_VCCRX/TX | VTRx+ 2.5 V input supply |

13.17. VLDB+ electrical characteristics¶

| Symbol | Parameter | Min | Max | Units |

|---|---|---|---|---|

| VIN_EXT | External power supply | 10 | 12 | V |

| P12V0_FMC | FMC power supply | 12 | 12 | V |

| VADJ | FPGA Voltage adjust | 1.13 | 1.32 | V |

| I_VLDB+ | Current consumption | 105 | 130 | mA |

Note

I_VLDB+: With both FEASTMP, in Standalone mode, 10 V input voltage, VTRx+ connected, lpGBT programmed with Quickstart configuration and locked.

13.18. Constraints file¶

Here we provide a tested .xdc file of a VC707 Evaluation Kit with the pin connections between a VLDB+ and the two FMC.

#ECLK signals set_property PACKAGE_PIN J40 [get_ports {ECLK_P[1]}] set_property PACKAGE_PIN J41 [get_ports {ECLK_N[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[1]}] set_property PACKAGE_PIN K29 [get_ports {ECLK_P[2]}] set_property PACKAGE_PIN K30 [get_ports {ECLK_N[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[2]}] set_property PACKAGE_PIN V30 [get_ports {ECLK_P[3]}] set_property PACKAGE_PIN V31 [get_ports {ECLK_N[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[3]}] set_property PACKAGE_PIN L31 [get_ports {ECLK_P[4]}] set_property PACKAGE_PIN K32 [get_ports {ECLK_N[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[4]}] set_property PACKAGE_PIN M36 [get_ports {ECLK_P[5]}] set_property PACKAGE_PIN L37 [get_ports {ECLK_N[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[5]}] set_property PACKAGE_PIN R28 [get_ports {ECLK_P[6]}] set_property PACKAGE_PIN P28 [get_ports {ECLK_N[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[6]}] set_property PACKAGE_PIN N39 [get_ports {ECLK_P[7]}] set_property PACKAGE_PIN N40 [get_ports {ECLK_N[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[7]}] set_property PACKAGE_PIN F40 [get_ports {ECLK_P[8]}] set_property PACKAGE_PIN F41 [get_ports {ECLK_N[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[8]}] set_property PACKAGE_PIN R40 [get_ports {ECLK_P[9]}] set_property PACKAGE_PIN P40 [get_ports {ECLK_N[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[9]}] set_property PACKAGE_PIN R42 [get_ports {ECLK_P[10]}] set_property PACKAGE_PIN P42 [get_ports {ECLK_N[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[10]}] set_property PACKAGE_PIN N38 [get_ports {ECLK_P[11]}] set_property PACKAGE_PIN M39 [get_ports {ECLK_N[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[11]}] set_property PACKAGE_PIN M41 [get_ports {ECLK_P[12]}] set_property PACKAGE_PIN L41 [get_ports {ECLK_N[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[12]}] set_property PACKAGE_PIN G41 [get_ports {ECLK_P[13]}] set_property PACKAGE_PIN G42 [get_ports {ECLK_N[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[13]}] set_property PACKAGE_PIN M37 [get_ports {ECLK_P[14]}] set_property PACKAGE_PIN M38 [get_ports {ECLK_N[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[14]}] set_property PACKAGE_PIN H40 [get_ports {ECLK_P[15]}] set_property PACKAGE_PIN H41 [get_ports {ECLK_N[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[15]}] set_property PACKAGE_PIN P35 [get_ports {ECLK_P[16]}] set_property PACKAGE_PIN P36 [get_ports {ECLK_N[16]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[16]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[16]}] set_property PACKAGE_PIN W32 [get_ports {ECLK_P[17]}] set_property PACKAGE_PIN W33 [get_ports {ECLK_N[17]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[17]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[17]}] set_property PACKAGE_PIN R38 [get_ports {ECLK_P[18]}] set_property PACKAGE_PIN R39 [get_ports {ECLK_N[18]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[18]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[18]}] set_property PACKAGE_PIN AB41 [get_ports {ECLK_P[19]}] set_property PACKAGE_PIN AB42 [get_ports {ECLK_N[19]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[19]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[19]}] set_property PACKAGE_PIN U36 [get_ports {ECLK_P[20]}] set_property PACKAGE_PIN T37 [get_ports {ECLK_N[20]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[20]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[20]}] set_property PACKAGE_PIN AD38 [get_ports {ECLK_P[21]}] set_property PACKAGE_PIN AE38 [get_ports {ECLK_N[21]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[21]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[21]}] set_property PACKAGE_PIN Y42 [get_ports {ECLK_P[22]}] set_property PACKAGE_PIN AA42 [get_ports {ECLK_N[22]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[22]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[22]}] set_property PACKAGE_PIN AL41 [get_ports {ECLK_P[23]}] set_property PACKAGE_PIN AL42 [get_ports {ECLK_N[23]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[23]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[23]}] set_property PACKAGE_PIN AB38 [get_ports {ECLK_P[24]}] set_property PACKAGE_PIN AB39 [get_ports {ECLK_N[24]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[24]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[24]}] set_property PACKAGE_PIN AJ42 [get_ports {ECLK_P[25]}] set_property PACKAGE_PIN AK42 [get_ports {ECLK_N[25]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[25]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[25]}] set_property PACKAGE_PIN AD40 [get_ports {ECLK_P[26]}] set_property PACKAGE_PIN AD41 [get_ports {ECLK_N[26]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[26]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[26]}] set_property PACKAGE_PIN U32 [get_ports {ECLK_P[27]}] set_property PACKAGE_PIN U33 [get_ports {ECLK_N[27]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[27]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[27]}] set_property PACKAGE_PIN P30 [get_ports {ECLK_P[28]}] set_property PACKAGE_PIN N31 [get_ports {ECLK_N[28]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_P[28]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {ECLK_N[28]}] #EDIN signals set_property PACKAGE_PIN J31 [get_ports {EDIN_P[0]}] set_property PACKAGE_PIN H31 [get_ports {EDIN_N[0]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[0]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[0]}] set_property PACKAGE_PIN L29 [get_ports {EDIN_P[1]}] set_property PACKAGE_PIN L30 [get_ports {EDIN_N[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[1]}] set_property PACKAGE_PIN R30 [get_ports {EDIN_P[2]}] set_property PACKAGE_PIN P31 [get_ports {EDIN_N[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[2]}] set_property PACKAGE_PIN M28 [get_ports {EDIN_P[3]}] set_property PACKAGE_PIN M29 [get_ports {EDIN_N[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[3]}] set_property PACKAGE_PIN U31 [get_ports {EDIN_P[4]}] set_property PACKAGE_PIN T31 [get_ports {EDIN_N[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[4]}] set_property PACKAGE_PIN V29 [get_ports {EDIN_P[5]}] set_property PACKAGE_PIN U29 [get_ports {EDIN_N[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[5]}] set_property PACKAGE_PIN J30 [get_ports {EDIN_P[6]}] set_property PACKAGE_PIN H30 [get_ports {EDIN_N[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[6]}] set_property PACKAGE_PIN N28 [get_ports {EDIN_P[7]}] set_property PACKAGE_PIN N29 [get_ports {EDIN_N[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[7]}] set_property PACKAGE_PIN Y29 [get_ports {EDIN_P[8]}] set_property PACKAGE_PIN Y30 [get_ports {EDIN_N[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[8]}] set_property PACKAGE_PIN W30 [get_ports {EDIN_P[9]}] set_property PACKAGE_PIN W31 [get_ports {EDIN_N[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[9]}] set_property PACKAGE_PIN K37 [get_ports {EDIN_P[10]}] set_property PACKAGE_PIN K38 [get_ports {EDIN_N[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[10]}] set_property PACKAGE_PIN H39 [get_ports {EDIN_P[11]}] set_property PACKAGE_PIN G39 [get_ports {EDIN_N[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[11]}] set_property PACKAGE_PIN K42 [get_ports {EDIN_P[12]}] set_property PACKAGE_PIN J42 [get_ports {EDIN_N[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[12]}] set_property PACKAGE_PIN M42 [get_ports {EDIN_P[13]}] set_property PACKAGE_PIN L42 [get_ports {EDIN_N[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[13]}] set_property PACKAGE_PIN P41 [get_ports {EDIN_P[14]}] set_property PACKAGE_PIN N41 [get_ports {EDIN_N[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[14]}] set_property PACKAGE_PIN K39 [get_ports {EDIN_P[15]}] set_property PACKAGE_PIN K40 [get_ports {EDIN_N[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[15]}] set_property PACKAGE_PIN AF41 [get_ports {EDIN_P[16]}] set_property PACKAGE_PIN AG41 [get_ports {EDIN_N[16]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[16]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[16]}] set_property PACKAGE_PIN W40 [get_ports {EDIN_P[17]}] set_property PACKAGE_PIN Y40 [get_ports {EDIN_N[17]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[17]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[17]}] set_property PACKAGE_PIN AJ40 [get_ports {EDIN_P[18]}] set_property PACKAGE_PIN AJ41 [get_ports {EDIN_N[18]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[18]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[18]}] set_property PACKAGE_PIN Y39 [get_ports {EDIN_P[19]}] set_property PACKAGE_PIN AA39 [get_ports {EDIN_N[19]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[19]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[19]}] set_property PACKAGE_PIN AC38 [get_ports {EDIN_P[20]}] set_property PACKAGE_PIN AC39 [get_ports {EDIN_N[20]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[20]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[20]}] set_property PACKAGE_PIN AJ38 [get_ports {EDIN_P[21]}] set_property PACKAGE_PIN AK38 [get_ports {EDIN_N[21]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[21]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[21]}] set_property PACKAGE_PIN AC40 [get_ports {EDIN_P[22]}] set_property PACKAGE_PIN AC41 [get_ports {EDIN_N[22]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[22]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[22]}] set_property PACKAGE_PIN AD42 [get_ports {EDIN_P[23]}] set_property PACKAGE_PIN AE42 [get_ports {EDIN_N[23]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[23]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[23]}] set_property PACKAGE_PIN U37 [get_ports {EDIN_P[24]}] set_property PACKAGE_PIN U38 [get_ports {EDIN_N[24]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[24]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[24]}] set_property PACKAGE_PIN V33 [get_ports {EDIN_P[25]}] set_property PACKAGE_PIN V34 [get_ports {EDIN_N[25]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[25]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[25]}] set_property PACKAGE_PIN AK39 [get_ports {EDIN_P[26]}] set_property PACKAGE_PIN AL39 [get_ports {EDIN_N[26]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[26]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[26]}] set_property PACKAGE_PIN AF42 [get_ports {EDIN_P[27]}] set_property PACKAGE_PIN AG42 [get_ports {EDIN_N[27]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_P[27]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDIN_N[27]}] #EDOUT signals set_property PACKAGE_PIN C33 [get_ports {EDOUT_P[0]}] set_property PACKAGE_PIN C34 [get_ports {EDOUT_N[0]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[0]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[0]}] set_property PACKAGE_PIN B39 [get_ports {EDOUT_P[1]}] set_property PACKAGE_PIN A39 [get_ports {EDOUT_N[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[1]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[1]}] set_property PACKAGE_PIN E37 [get_ports {EDOUT_P[2]}] set_property PACKAGE_PIN E38 [get_ports {EDOUT_N[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[2]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[2]}] set_property PACKAGE_PIN B37 [get_ports {EDOUT_P[3]}] set_property PACKAGE_PIN B38 [get_ports {EDOUT_N[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[3]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[3]}] set_property PACKAGE_PIN H38 [get_ports {EDOUT_P[4]}] set_property PACKAGE_PIN G38 [get_ports {EDOUT_N[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[4]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[4]}] set_property PACKAGE_PIN J37 [get_ports {EDOUT_P[5]}] set_property PACKAGE_PIN J38 [get_ports {EDOUT_N[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[5]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[5]}] set_property PACKAGE_PIN B36 [get_ports {EDOUT_P[6]}] set_property PACKAGE_PIN A37 [get_ports {EDOUT_N[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[6]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[6]}] set_property PACKAGE_PIN J36 [get_ports {EDOUT_P[7]}] set_property PACKAGE_PIN H36 [get_ports {EDOUT_N[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[7]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[7]}] set_property PACKAGE_PIN G36 [get_ports {EDOUT_P[8]}] set_property PACKAGE_PIN G37 [get_ports {EDOUT_N[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[8]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[8]}] set_property PACKAGE_PIN C38 [get_ports {EDOUT_P[9]}] set_property PACKAGE_PIN C39 [get_ports {EDOUT_N[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[9]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[9]}] set_property PACKAGE_PIN F34 [get_ports {EDOUT_P[10]}] set_property PACKAGE_PIN F35 [get_ports {EDOUT_N[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[10]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[10]}] set_property PACKAGE_PIN E33 [get_ports {EDOUT_P[11]}] set_property PACKAGE_PIN D33 [get_ports {EDOUT_N[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[11]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[11]}] set_property PACKAGE_PIN H33 [get_ports {EDOUT_P[12]}] set_property PACKAGE_PIN G33 [get_ports {EDOUT_N[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[12]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[12]}] set_property PACKAGE_PIN G32 [get_ports {EDOUT_P[13]}] set_property PACKAGE_PIN F32 [get_ports {EDOUT_N[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[13]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[13]}] set_property PACKAGE_PIN E34 [get_ports {EDOUT_P[14]}] set_property PACKAGE_PIN E35 [get_ports {EDOUT_N[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[14]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[14]}] set_property PACKAGE_PIN D35 [get_ports {EDOUT_P[15]}] set_property PACKAGE_PIN D36 [get_ports {EDOUT_N[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_P[15]}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {EDOUT_N[15]}] #Slow Control signals set_property PACKAGE_PIN AC31 [get_ports {ADC[0]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[0]}] set_property DRIVE 4 [get_ports {ADC[0]}] set_property PACKAGE_PIN AD31 [get_ports {ADC[1]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[1]}] set_property DRIVE 4 [get_ports {ADC[1]}] set_property PACKAGE_PIN AA31 [get_ports {ADC[2]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[2]}] set_property DRIVE 4 [get_ports {ADC[2]}] set_property PACKAGE_PIN AA32 [get_ports {ADC[3]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[3]}] set_property DRIVE 4 [get_ports {ADC[3]}] set_property PACKAGE_PIN AE29 [get_ports {ADC[4]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[4]}] set_property DRIVE 4 [get_ports {ADC[4]}] set_property PACKAGE_PIN AE30 [get_ports {ADC[5]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[5]}] set_property DRIVE 4 [get_ports {ADC[5]}] set_property PACKAGE_PIN AF31 [get_ports {ADC[6]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[6]}] set_property DRIVE 4 [get_ports {ADC[6]}] set_property PACKAGE_PIN AF32 [get_ports {ADC[7]}] set_property IOSTANDARD LVCMOS12 [get_ports {ADC[7]}] set_property DRIVE 4 [get_ports {ADC[7]}] set_property PACKAGE_PIN AE34 [get_ports VDAC] set_property IOSTANDARD LVCMOS12 [get_ports VDAC] set_property PACKAGE_PIN AE35 [get_ports {GPIO[0]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[0]}] set_property DRIVE 4 [get_ports {GPIO[0]}] set_property PACKAGE_PIN AF34 [get_ports {GPIO[1]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[1]}] set_property DRIVE 4 [get_ports {GPIO[1]}] set_property PACKAGE_PIN AG34 [get_ports {GPIO[2]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[2]}] set_property DRIVE 4 [get_ports {GPIO[2]}] set_property PACKAGE_PIN AE32 [get_ports {GPIO[3]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[3]}] set_property DRIVE 4 [get_ports {GPIO[3]}] set_property PACKAGE_PIN AE33 [get_ports {GPIO[4]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[4]}] set_property DRIVE 4 [get_ports {GPIO[4]}] set_property PACKAGE_PIN AF35 [get_ports {GPIO[5]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[5]}] set_property DRIVE 4 [get_ports {GPIO[5]}] set_property PACKAGE_PIN AF36 [get_ports {GPIO[6]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[6]}] set_property DRIVE 4 [get_ports {GPIO[6]}] set_property PACKAGE_PIN AE37 [get_ports {GPIO[7]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[7]}] set_property DRIVE 4 [get_ports {GPIO[7]}] set_property PACKAGE_PIN AF37 [get_ports {GPIO[8]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[8]}] set_property DRIVE 4 [get_ports {GPIO[8]}] set_property PACKAGE_PIN AG36 [get_ports {GPIO[9]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[9]}] set_property DRIVE 4 [get_ports {GPIO[9]}] set_property PACKAGE_PIN AH36 [get_ports {GPIO[10]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[10]}] set_property DRIVE 4 [get_ports {GPIO[10]}] set_property PACKAGE_PIN AC34 [get_ports {GPIO[11]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[11]}] set_property DRIVE 4 [get_ports {GPIO[11]}] set_property PACKAGE_PIN AD35 [get_ports {GPIO[12]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[12]}] set_property DRIVE 4 [get_ports {GPIO[12]}] set_property PACKAGE_PIN AB36 [get_ports {GPIO[13]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[13]}] set_property DRIVE 4 [get_ports {GPIO[13]}] set_property PACKAGE_PIN AB37 [get_ports {GPIO[14]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[14]}] set_property DRIVE 4 [get_ports {GPIO[14]}] set_property PACKAGE_PIN Y37 [get_ports {GPIO[15]}] set_property IOSTANDARD LVCMOS12 [get_ports {GPIO[15]}] set_property DRIVE 4 [get_ports {GPIO[15]}] set_property PACKAGE_PIN AA37 [get_ports RSTOUTB] set_property IOSTANDARD LVCMOS12 [get_ports RSTOUTB] set_property PACKAGE_PIN AD36 [get_ports M0SCL] set_property IOSTANDARD LVCMOS12 [get_ports M0SCL] set_property DRIVE 4 [get_ports M0SCL] set_property PACKAGE_PIN AA34 [get_ports M1SCL] set_property IOSTANDARD LVCMOS12 [get_ports M1SCL] set_property DRIVE 4 [get_ports M1SCL] set_property PACKAGE_PIN AD37 [get_ports M0SDA] set_property IOSTANDARD LVCMOS12 [get_ports M0SDA] set_property DRIVE 4 [get_ports M0SDA] set_property PACKAGE_PIN AA35 [get_ports M1SDA] set_property IOSTANDARD LVCMOS12 [get_ports M1SDA] set_property DRIVE 4 [get_ports M1SDA] #Phase Shifter clock signals set_property PACKAGE_PIN P37 [get_ports {PSCLK_P0}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_P0}] set_property PACKAGE_PIN P38 [get_ports {PSCLK_N0}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_N0}] set_property PACKAGE_PIN T32 [get_ports {PSCLK_P2}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_P2}] set_property PACKAGE_PIN R32 [get_ports {PSCLK_N2}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_N2}] set_property PACKAGE_PIN V35 [get_ports {PSCLK_P3}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_P3}] set_property PACKAGE_PIN V36 [get_ports {PSCLK_N3}] set_property IOSTANDARD DIFF_SSTL12_DCI [get_ports {PSCLK_N3}] #DCI cascade for 100 Ohm termination on differential set_property DCI_CASCADE {35} [get_iobanks 34] set_property DCI_CASCADE {17 18} [get_iobanks 19]