7. VLDB+ powering modes¶

In the VLDB+, there are 2 powering modes: The Standalone mode (external) and the FMC mode. As we already said,

the use of the FEASTMP DC/DCs is anyway mandatory in both modes.

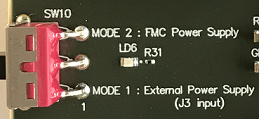

Fig. 7.1 SW10 to power the VLDB+¶

To power on the VLDB+ in one of the aforementioned modes, we have to switch the tri-state SW10. Move it to the bottom (MODE 1: External)

to power the VLDB+ in the Standalone mode, move it to the top (MODE 2: FMC) to power the VLDB+ in the FMC mode and move it to the middle

to turn it off.

7.1. Standalone mode¶

In the Standalone mode (referred as Mode 1 on SW10), the VLDB+ is powered through an external power supply.

In this mode, the recommended input voltage supply is 10 V (min 9.5 V, max 12 V).

The supply voltage has to be provided through the 2-pin Phoenix connector (provided with the VLDB+) connected to the J3.

7.1.1. FMC use in Standalone mode¶

In addition, if you connect one or several front-end boards to one or both FMC HPCs (instead of an FPGA evaluation kit) and set

the Standalone mode, the Front-end board(s) will be powered by the VLDB+ (P1V2) through the HPC_VIO_B_M2C pins. You can also connect a Front-end board that

doesn’t require any power just to take out the lpGBT signals. Obviously, connecting front end boards to the FMC

requires a full pin compatibility between the FE board and the VLDB+ (e-links, power, adc, etc). Refer to the Section 13

for more information.

7.2. FMC mode¶

In the FMC mode (referred as Mode 2 on SW10), an external FPGA Evaluation Kit has to be connected on both VLDB+ FMC HPC

connectors to power on the VLDB+.

In this mode, the FEASTMP inputs are being provided with the P12V0_FMC of the FMC standard.

| Evaluation Kit FPGA | Brand |

|---|---|

| VC707 | Xilinx |

| KCU105 | Xilinx |

| VCU108 | Xilinx |

| VCU118 | Xilinx |

| ZCU102 | Xilinx |

Note

Neither other Xilinx models nor Altera brand has been tested with the VLDB+ as they are not supposed to be compatible.

Note

When connecting the EK FPGA together with the VLDB+, please take a look to Section 9.1.1.